HCPL-0600-500E

OPTOISO 3.75KV OPN COLLECTOR 8SO

型号

HCPL-0600-500E

制造商/品牌

系列

-

零件状态

Active

包装

Tape & Reel (TR)

输入类型

DC

工作温度

-40°C ~ 85°C

安装类型

Surface Mount

封装/箱体

8-SOIC (0.154", 3.90mm Width)

输出类型

Open Collector, Schottky Clamped

通道数

1

供应商器件封装

8-SO Tall

电压 - 电源

4.5 V ~ 5.5 V

数据速率

10MBd

电流 - 输出/通道

50mA

电压 - 隔离

3750Vrms

上升/下降时间(典型值)

24ns, 10ns

输入 - 1 侧/2 侧

1/0

共模瞬变抗扰度(最小值)

5kV/µs

传播延迟 tpLH / tpHL (最大值)

100ns, 100ns

电压 - 正向 (Vf) (典型值)

1.5V

电流 - 直流正向 (If) (最大值)

20mA

请求报价

请填写所有必填字段并点击“提交”,我们将在12小时内通过电子邮件与您联系。如果您有任何问题,请留言或发送电子邮件至 1943626632@qq.com,我们将尽快回复。

有货 33400 PCS

联系信息

more_pkgimg

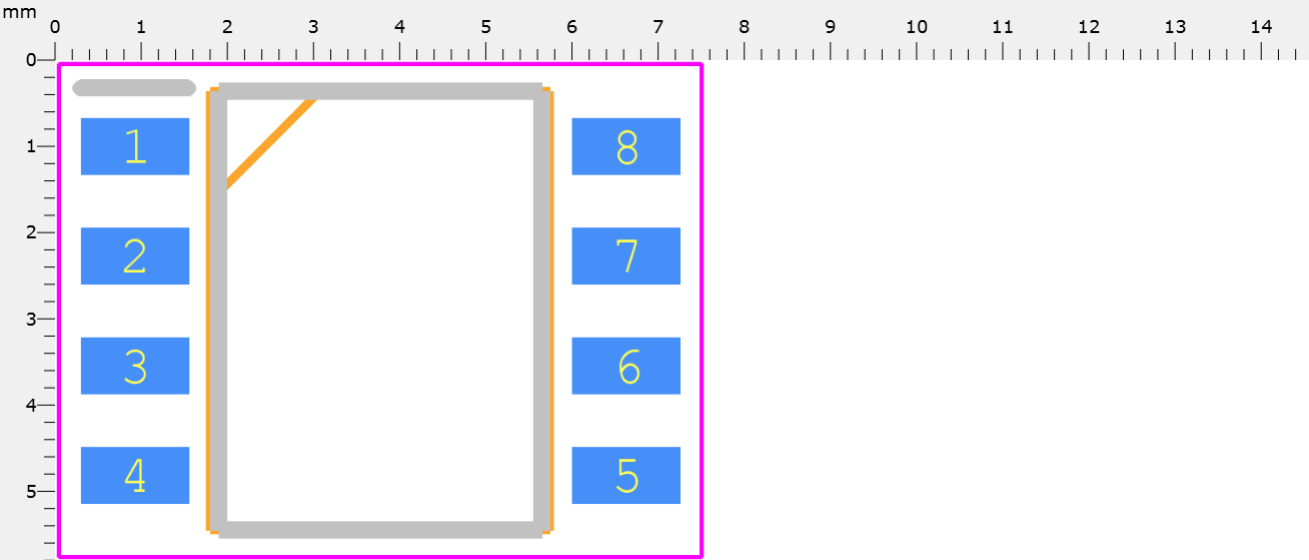

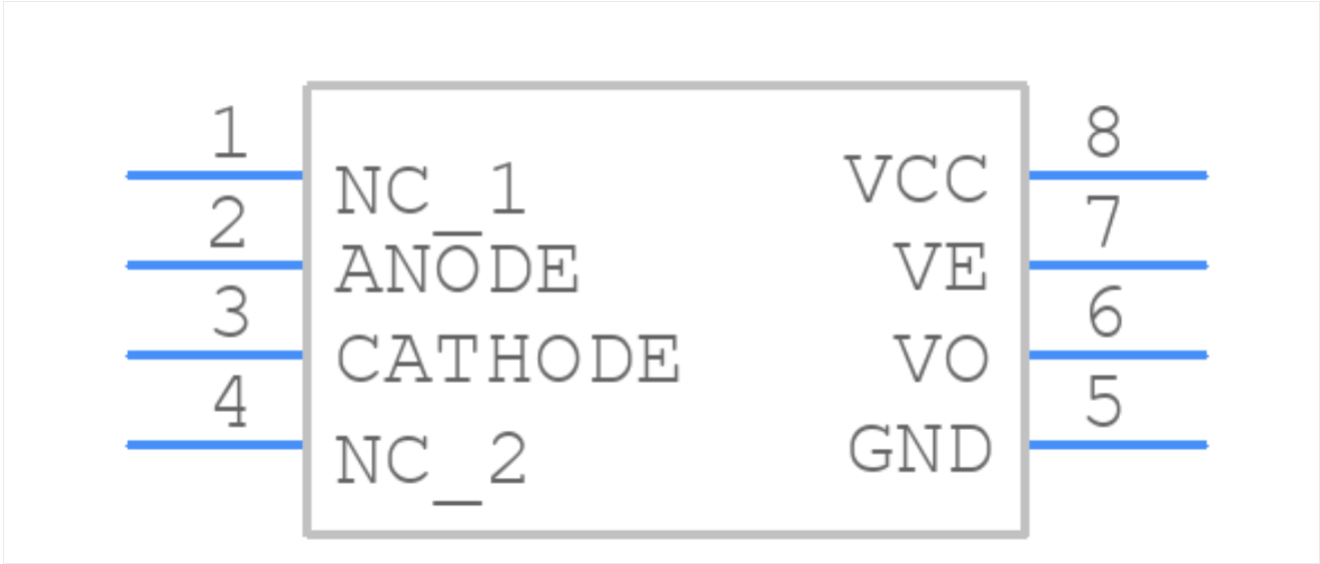

more_schimg

more_3dimg

more_desctext

High Speed Optocouplers 10MBd 1Ch 5mA

Pin Count--------8

Part Category--------Integrated Circuit

Package Category--------Small Outline Packages

Footprint Name--------Small Outline Packages - Small-Outline SO-8

Pin Count--------8

Part Category--------Integrated Circuit

Package Category--------Small Outline Packages

Footprint Name--------Small Outline Packages - Small-Outline SO-8

download_pdf

more_faq

HCPL-0600-500E Frequently Asked Questions (FAQs)

What is the recommended PCB layout for optimal performance of HCPL-0600-500E?

A good PCB layout for HCPL-0600-500E involves keeping the input and output traces separate, using a ground plane, and minimizing the length of the input traces. It's also recommended to use a 0.1uF capacitor between VCC and GND pins to filter out noise.

How do I ensure reliable operation of HCPL-0600-500E in high-temperature environments?

To ensure reliable operation of HCPL-0600-500E in high-temperature environments, it's essential to follow proper thermal management practices, such as providing adequate heat sinking, using thermal interface materials, and keeping the device within its recommended operating temperature range.

What are the ESD protection considerations for HCPL-0600-500E?

HCPL-0600-500E has built-in ESD protection, but it's still important to follow proper ESD handling procedures during assembly and testing. This includes using ESD-safe materials, grounding straps, and ionizers to minimize the risk of ESD damage.

Can I use HCPL-0600-500E in a high-vibration environment?

Yes, HCPL-0600-500E is designed to operate in high-vibration environments. However, it's essential to ensure that the device is properly secured to the PCB and that the PCB is designed to withstand the expected vibration levels.

What are the recommended soldering profiles for HCPL-0600-500E?

The recommended soldering profile for HCPL-0600-500E involves a peak temperature of 240°C, with a dwell time of 10-30 seconds. It's essential to follow the recommended soldering profile to prevent damage to the device.

What is the recommended PCB layout for optimal performance of HCPL-0600-500E?

A good PCB layout for HCPL-0600-500E involves keeping the input and output traces separate, using a ground plane, and minimizing the length of the input traces. It's also recommended to use a 0.1uF capacitor between VCC and GND pins to filter out noise.

How do I ensure reliable operation of HCPL-0600-500E in high-temperature environments?

To ensure reliable operation of HCPL-0600-500E in high-temperature environments, it's essential to follow proper thermal management practices, such as providing adequate heat sinking, using thermal interface materials, and keeping the device within its recommended operating temperature range.

What are the ESD protection considerations for HCPL-0600-500E?

HCPL-0600-500E has built-in ESD protection, but it's still important to follow proper ESD handling procedures during assembly and testing. This includes using ESD-safe materials, grounding straps, and ionizers to minimize the risk of ESD damage.

Can I use HCPL-0600-500E in a high-vibration environment?

Yes, HCPL-0600-500E is designed to operate in high-vibration environments. However, it's essential to ensure that the device is properly secured to the PCB and that the PCB is designed to withstand the expected vibration levels.

What are the recommended soldering profiles for HCPL-0600-500E?

The recommended soldering profile for HCPL-0600-500E involves a peak temperature of 240°C, with a dwell time of 10-30 seconds. It's essential to follow the recommended soldering profile to prevent damage to the device.

关键词 HCPL-0600-500E

HCPL-0600-500E 电子元件

HCPL-0600-500E 销售

HCPL-0600-500E 供应商

HCPL-0600-500E 分销商

HCPL-0600-500E 数据表

HCPL-0600-500E 图片

HCPL-0600-500E 报价

HCPL-0600-500E 提供

HCPL-0600-500E 最低价格

HCPL-0600-500E 搜索

HCPL-0600-500E 购买

HCPL-0600-500E 芯片

×

![]()